TMS320VC5416�����Y��

TMS320VC5416���c:������www.ytjinfuren.com�����ṩ�����փ�(n��i)�݁�Դ�ھW(w��ng)�j(lu��)�������ַ�����ę�(qu��n)��Ո�c�҂�(li��n)ϵ������

�����M(j��n)�Ķ࿂���ܘ�(g��u)���xͨ�^

�Ϊ���16λ��(sh��)��(j��)�惦��������һ�������в��д惦���\��ָ��

����惦��������(li��n)ؓ(f��)�d

2 ���l���惦ָ��

" se="�� 40-Bit Arithmetic Logic Unit (ALU) Including a �� Conditional Store Instructions">�� 40λ���g(sh��)߉��Ԫ��ALU�� 2 ���l���惦ָ��

2 ���l���惦ָ��

40λͰʽ��λ���̓ɂ������ď��Д��40λ�ۼ��������ٷ���

40λ���÷���ˮ���l(f��)�����Ϳɾ��̆����ڳ˷��ӷ���/�ۼӣ�MAC�����y�н��Q

" se="�� On-Chip Peripherals �� 17- ´ 17-Bit Parallel Multiplier Coupled to a �C Software-Programmable Wait-State 40-Bit Dedicated Adder for Non-Pipelined Generator and Programmable Single-Cycle Multiply/Accumulate (MAC) Bank-Switching">���P(gu��n)��Ƭ�����O(sh��)�� 17 - '17λ���г˷�������һ�� - ܛ���ɾ��̵ȴ� 40λ���÷���ˮ���l(f��)�����Ϳɾ��̆����ڳ˷��ӷ���/�ۼӣ�MAC�����y�н��Q

40λ���÷���ˮ���l(f��)�����Ϳɾ��̆����ڳ˷��ӷ���/�ۼӣ�MAC�����y�н��Q

���� - Ƭ�Ͽɾ����i��h(hu��n)

�����^���x��ʹ惦��Ԫ�Ļ�·��PLL���c�ⲿ�r犰l(f��)������CSSU��

����/�S�ر�����^�r�Դ�x��

�����a��������Ӌ��ָ��(sh��)��ָ��(sh��) - һ��16λ���r��

�rֵ��40λ�ۼ����ărֵ - ��ͨ��ֱ�Ӵ惦���L����DMA��

�����ڿ���

���p��ַ���ɰ˂��o�� - ����ͨ�����_���ж˿�

�Ĵ����̓ɂ��o���Ĵ�����McBSP�ģ�

���g(sh��)��Ԫ��ARAUs�� - 8/16-Bit�����������C�˿�

����(sh��)��(j��)������һ�����������˹��ܽӿڣ�HPI8/16��

���Uչ��ַģʽ800�f��16λ�������S��IDLE1���Ŀ��ƣ����Ɍ�ַ�ⲿ����IDLE2�����g���ģʽ��IDLE3�f��

�� 128K�ĵ�16λƬ��RAM�ĽM�ɣ��P(gu��n)���ơ� CLKOUT�Ľ��Î�CLKOUT

- �˞�8K��16λ�KƬ����(n��i)�û��ڒ���ķ���߉������IEEE

�Բ�1149.1��JTAG��߅�����߉��1���p�L������/��(sh��)��(j��)RAM

- �˞�8K��16λ�KƬ�� 144���_�����У�BGA����GGU��Y��

���L������RAM �� 144���_С�����ķ���ƽ���b

�� 16K�ĵ�16λƬ��ROM�ģ�LQFP���b�����K���Y������

����惦���� 6.25 - ns�����ڶ��cָ��

���������ⲿ���нӿڣ�XIO2���Ĉ�(zh��)�Еr�g��160 MIPS����

����ָ����؏�(f��)�͉K�؏�(f��)�� 8.33 - ns�����ڶ��cָ��

�\��������a�Ĉ�(zh��)�Еr�g��120 MIPS����

���K�惦������ָ�����á� 3.3��VI / O�Դ늉���160��120��MIPS��

����͔�(sh��)��(j��)������ 1.6 V��(n��i)���Դ늉���160 MIPS����

�S��32λ�L��Word���P(gu��n)�f��������(sh��)�� 1.5 - V�ĺ��Ĺ��늉���120 MIPS����

�c�ɂ�������������(sh��)��1��IEEE��(bi��o)��(zh��n)1149.1-1990��(bi��o)��(zh��n)ԇ����˿ں����P(gu��n)�f��

߅�����Y(ji��)��(g��u)������www.ytjinfuren.com�����ṩ�����փ�(n��i)�݁�Դ�ھW(w��ng)�j(lu��)�������ַ�����ę�(qu��n)��Ո�c�҂�(li��n)ϵ������

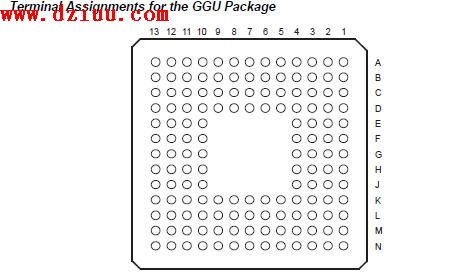

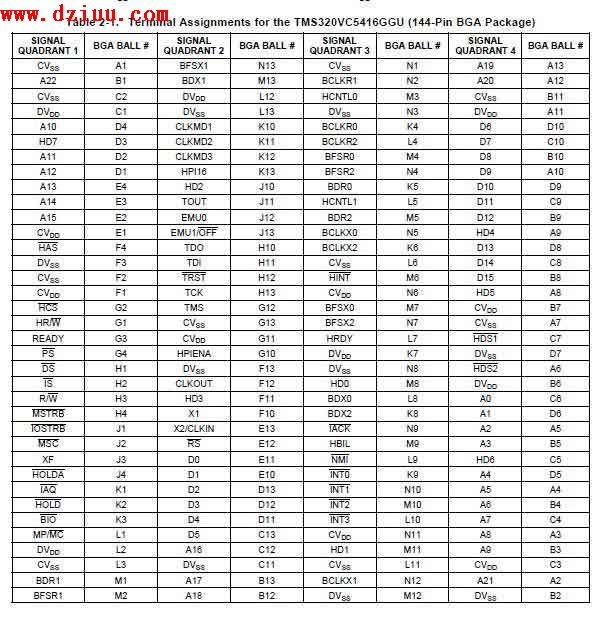

TMS320VC5416��GGU�����ӷ���D:

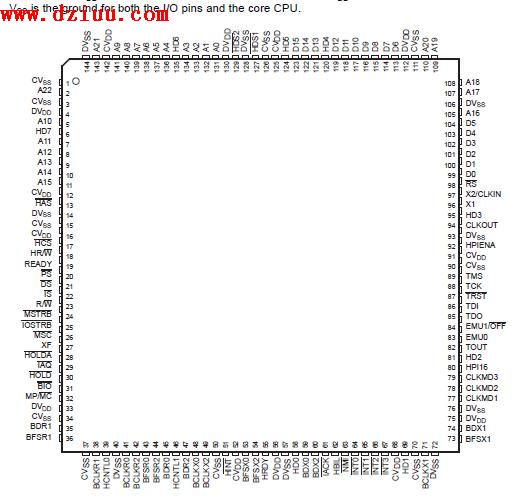

���_���ܷ���D:

���ĵ�ַ��http://www.ytjinfuren.com/dz/26/20101026214543.shtml

����(bi��o)��:

- ��һƪ���£���ɫ�h(hu��n)�����ֵӋ����_�ھ�Ӌ�㹤��

- ��һƪ���£�SAA5542�����Y�ϡ����_����

-

TMS320VC5416�����Y��

TMS320VC5416�����Y��

�o

������dȤ��

- ���]��(n��i)��

- ����(n��i)��

-

- �oԴ�����x�� 2024-10-10

- ACM6755 ֧��3������(y��ng)�õ�ȫ��������ֱ���oˢ늙C�(q��)��IC���� 2024-10-09

- YXC�����Q�����������I(y��)���C��(y��ng)�� 2024-09-27

- ��Դ����͟oԴ����ą^(q��)�e 2024-09-24

- ��ģ�K��Ȳ��p����ѕr�lCP-��־��� 2024-09-20

- ���w�C�����Ĺ���ԭ�� 2024-09-19

- YXCʯӢ��Դ��ֿɾ��̾����l�c200MHZ��С��(sh��)�c�ɾ��_����6λ����(y��ng)����5G��վ 2024-09-12

- 70V�͉����{(di��o)OVP�ֵ���^�����o(h��)о-ƽоPW1600 2024-09-05

- YXC�P�d��Դ��Ʒ�l(f��)��ح1.2V�����ĕr犽�Q���� 2024-09-05

- YXC�P�d | 32.768KHZ�����x�ͷ��� 2024-09-02

- ���T��(bi��o)��

-

���ż����· ������·�D LED ���l�Ŵ����·�D ��Ƭ�C 늙C���� LED�·�D ��(w��n)���Դ �_�P(gu��n)��(w��n)���Դ ����·�D ׃�l�� ��׃�� LED�����· ���{(di��o)�S���g(sh��) LED�(q��)���·�D AV�Ŵ����· �ص����·�D 555���r�� 늴Št�·�D ��(w��n)�������· 51��Ƭ�C �·�O(sh��)Ӌ �^�����o(h��)�· �^�����o(h��)�· ��(w��n)���· �ھ�Ӌ�� ���˷�(w��n)���· ��·���o(h��)�· �ŷ�늙C ���M(j��n)늙C PIC��Ƭ�C ֱ����(w��n)���Դ ���{(di��o)��(w��n)���Դ EMC ©늱��o(h��)�· Ƕ��ʽϵ�y(t��ng) ��Ȧ ���l��׃�� ���� ���{(di��o) UPS DC-DC�· �ضȂ����� 늴ż��� ���� ���l�_�P(gu��n)�Դ ���� EMI ��˹�� ���⾀