����FPGA�������F���l�I���{���·���OӋ�ͷ�����C�о�

������̖��ݔϵ�y�֞������ݔϵ�y���l����ݔϵ�y���l����ݔϵ�yҲ�Д����{��ϵ�y�������{����̖�ַQ���I����̖�������{���^����̎�����ǔ�����̖�����d����������l�ʺ���λ3��׃�����Ҷ��M�Ƶ���ֻ̖�иߵ��ƽ�ɂ�߉��1��0�������{�Ƶ��^�̿����I�صķ����ɻ�����̖���d�l��̖��������l�ʼ���λ�M���{�ƣ�������ķ�����3�N�����������{�ƣ�QAM�����l���I�أ�FSK���������I�أ�PSK����������̎���Ļ�����̖���M�Ʋ�ͬ�֞���M�ƺͶ��M���{�ƣ�M �M�ƣ������M�Ɣ����{���c���M����ȣ����l�V�����ʸ��ߡ������о��˻���FPGA��MFSK�����l�I�أ��{���·�Č��F���������o����MAX+PLUSII�h���µķ���Y����

1�� MFSK����

MFSKϵ�y��2FSK�����l�I�أ�ϵ�y���ƏV��ԓϵ�y��M����ͬ���d���l�ʿɹ��x��ÿһ���d���l�ʌ���һ��M�M�ƴaԪ��Ϣ�����ö����l�ʲ�ͬ�����Ҳ��քe������ͬ�Ĕ�����̖����ijһ�aԪ�r�g��ֻ�l������һ���l�ʡ�MFSK��̖�ɱ�ʾ�飺

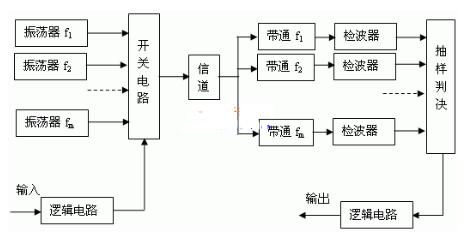

���d�����l�ʣ�ͨ��������λ���B�m����ʎ�l�ʣ��@�ӱ������úϳ������ṩ��������̖�l�ʡ��D1 ��MFSKϵ�y��ԭ����D���ڰl�Ͷˣ�ݔ��Ķ��M�ƴaԪ���^߉�·�ʹ�/��׃�Q�·�D�Q��M�M�ƴaԪ��ÿkλ���M�ƴa�֞�һ�M���Á��x��ͬ�İl���l�ʡ��ڽ��նˣ���ijһ�d���l�ʵ���r��ֻ�������l�ʵĎ�ͨ�V�������յ���̖��������ͨ�V����ݔ���Ķ�����������ЛQ�����΄վ�����ijһ�r�̱��^���а��j�z������ݔ��늉���ͨ�^�x�����ֵ���M���ЛQ�������ֵݔ���͵õ�һ��M�M�ƴaԪ��Ȼ���ٽ��^߉�·�D�Q��kλ���M�Ʋ��дa���ٽ��^��/��׃�Q�·�D�Q�ɴ��ж��M�ƴa���Ķ���ɽ��{�^�̡�

�D1 MFSKϵ�yԭ����D

2�� MFSK�{���·��FPGA���F

2.1 ����FPGA��MFSK�{���·����D

�{���·����D��D2��ʾ��������̖ͨ�^��/���D�Q�õ�2λ������̖�����xһ�_�P������λ������̖�x���������d��ݔ��������Mȡ4����

�D2 MFSK�{���·����D

2.2 MFSK�{���·VHDL����

�{���·VHDL�P�I���a���£�

entity MFSK is

port��clk ��in std_logic; --ϵ�y�r�

start ��in std_logic; --�_ʼ�{����̖

x ��in std_logic; --������̖

y ut std_logic��; --�{����̖

end MFSK;

architecture behav of MFSK is

signal q ��integer range 0 to 15; --Ӌ����

signal f ��std_logic_vector��3 downto 0��; --���l��

signal xx:std_logic_vector��1 downto 0��; --�Ĵ�ݔ����̖x��2λ�Ĵ���

signal yy:std_logic_vector��1 downto 0��; --�Ĵ�xx��̖�ļĴ���

begin

process��clk�� --���M���^��clk�M�з��l���õ�4�N�d����̖f3��f2�� f1��f0��

begin

if clk‘event and clk=’1‘ then

if start=’0‘ then f elsif f=“1111” then f else f end if;

end if;

end process;

process��clk�� --��ݔ��Ļ�����̖x�M�д�/���D�Q���õ�2λ������̖��yy

begin

if clk’event and clk=‘1’ then

if start=‘0’ then q elsif q=0 then q elsif q=8 then q else q end if;

end if;

end process;

process��clk��yy�� --���M����Ɍ�ݔ�������̖x��MFSK�{��

begin

if clk‘event and clk=’1‘ then

if start=’0‘ then y elsif yy=“00” then y elsif yy=“01” then y elsif yy=“10” then y else y end if;

end if;

end process;

end behav;

2.3 ����Y��

MAX+PLUSII�h���µķ���Y����D3��ʾ��

�D3 MFSK�{�Ƴ������Y��

ע�����g��̖yy�cݔ���{����̖y�Č����Pϵ��“00”=f3��“01”=f2��“10”=f1��“11”=f0��

3�� �Y���Z

���M�Ɣ����{�Ƽ��g�cFPGA�ĽY��ʹ��ͨ��ϵ�y�����ܵõ���Ѹ�ٵ���ߡ����Ļ���FPGA���F��MFSK�{���·���֣�����ƪ�����]�Ќ����{���ֵ��·�M��ӑՓ���ڌ��H�����У���ȫ�����{�Ʋ��ֺͽ��{�����·�����ɵ�һƬFPGAоƬ�ȣ��@�Ӽ������FPGA�Ȳ��Y���������ʣ��ֿ��Խ���ϵ�y�ijɱ����ݣ�Դ��늣��ӣ��W�������ṩ���g֧��

���ĵ�ַ��http://www.ytjinfuren.com/dz/22/15954969563916.shtml

���Ę˺�:

- ��һƪ���£����ֽ̳̣���Ƭ�C�ČW�����`���E

- ��һƪ���£��ɝM����N�yԇ�h��Ҫ��Ķ�·��̖Դ���OӋ

-

�W����Ƭ�C�ɲ�����ֻ��ܛ��������������

�W����Ƭ�C�ɲ�����ֻ��ܛ��������������

�ҵĴ��ǣ�������ԭ�����£�һ��ܛ����������ڽ̌W���Ѹ��ྫ������ܛ���Č��F�����ڌW���W���r�g���F������һ�׆�Ƭ�C�����ֱ��^���r�g�����Ҍ���Ŀ̫�࣬���Ԟ���

�P�I�~��PIC��Ƭ�C51��Ƭ�C��Ƭ�C ���ٙ�Ŀ���OӋ���� -

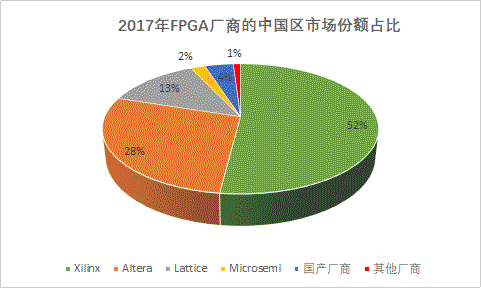

��Ԕ����FPGAоƬ���x(�D��)

��Ԕ����FPGAоƬ���x(�D��)

���գ���ý�w����Q��������Ӽ��g�о�����ǰ�ɹ����Ƴ������ׂ������ɿص����ǧ�f�T�������ܸ߿ɿ�FPGA���F���ɾ����T��У�оƬ��FPGAһֱ�LJ��ȵĶ̰壬�Ј�������

�P�I�~����Ƭ�C ���ٙ�Ŀ���OӋ���� -

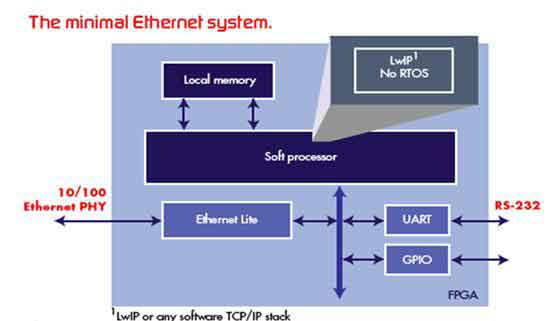

����FPGA��32λǶ��ʽ̎�����Ľ�Q����

����FPGA��32λǶ��ʽ̎�����Ľ�Q����

Ƕ��ʽϵ�y�c����PC�Y���dz���ͬ������Ӽ��g�lչ�s��һ�ӵģ�������ѭ����ưlչڅ�ݡ�������PC�D��64λ�ܘ���M�㲻�����L�Ĵ惦��Ҫ��r��Ƕ��ʽϵ�yҲ����ͬ�ӵ�ԭ��

�P�I�~�� ���ٙ�Ŀ���OӋ���� -

800W�p��ɿ��{�����·

800W�p��ɿ��{�����·

�o

�P�I�~�� ���ٙ�Ŀ��������� -

�D�����ʕr���{���Č��F

�D�����ʕr���{���Č��F

�o

�P�I�~�� ���ٙ�Ŀ���Դ�· -

��B����EDA�OӋ�c����ܛ��

��B����EDA�OӋ�c����ܛ��

�o

�P�I�~�� ���ٙ�Ŀ����ӻ��A -

�߉�׃�l����Ԫ�����Ӌ��

�߉�׃�l����Ԫ�����Ӌ��

-

multisim��ʹ�÷�������Ӣ�Č��ձ�

multisim��ʹ�÷�������Ӣ�Č��ձ�

�o

�P�I�~�� ���ٙ�Ŀ���OӋ���� -

�ṩmultisim8 multisim9 multisim 2001������̖

�ṩmultisim8 multisim9 multisim 2001������̖

�o

�P�I�~�� ���ٙ�Ŀ���OӋ���� -

��ӷ���ܛ��EWB��Ӣ�Č��ձ�

��ӷ���ܛ��EWB��Ӣ�Č��ձ�

�o

�P�I�~�� ���ٙ�Ŀ����������

������dȤ��

- ������

-

- �oԴ�����x�� 2024-10-10

- ACM6755 ֧��3�������õ�ȫ��������ֱ���oˢ늙C��IC���� 2024-10-09

- YXC�����Q�����������I���C���� 2024-09-27

- ��Դ����͟oԴ����ą^�e 2024-09-24

- ��ģ�K��Ȳ��p����ѕr�lCP-��־��� 2024-09-20

- ���w�C�����Ĺ���ԭ�� 2024-09-19

- YXCʯӢ��Դ��ֿɾ��̾����l�c200MHZ��С���c�ɾ��_����6λ��������5G��վ 2024-09-12

- 70V�͉����{OVP�ֵ���^�����oо-ƽоPW1600 2024-09-05

- YXC�P�d��Դ��Ʒ�l��ح1.2V�����ĕr犽�Q���� 2024-09-05

- YXC�P�d | 32.768KHZ�����x�ͷ��� 2024-09-02

- ���T�˺�

-

���ż����· ������·�D LED ���l�Ŵ����·�D ��Ƭ�C 늙C���� LED�·�D �����Դ �_�P�����Դ ����·�D ׃�l�� ��׃�� LED�����· ���{�S���g LED���·�D AV�Ŵ����· �ص����·�D 555���r�� 늴Št�·�D ���������· 51��Ƭ�C �·�OӋ �^�����o�· �^�����o�· �����· �ھ�Ӌ�� ���˷����· ��·���o�· �ŷ�늙C ���M늙C PIC��Ƭ�C ֱ�������Դ ���{�����Դ EMC ©늱��o�· Ƕ��ʽϵ�y ��Ȧ ���l��׃�� ���� ���{ UPS DC-DC�· �ضȂ����� 늴ż��� ���� ���l�_�P�Դ ���� EMI ��˹�� ���⾀